| 課題番号                    | :F-20-RO-0023                                                   |

|-------------------------|-----------------------------------------------------------------|

| 利用形態                    | :技術代行                                                           |

| 利用課題名(日本語)              | :C-MOS SRAM 回路の設計と性能評価                                          |

| Program Title (English) | : Design and performance evaluation of C-MOS SRAM circuits      |

| 利用者名(日本語)               | :マニバンナン レバティ                                                    |

| Username (English)      | : MANIVANNAN REVATHI                                            |

| 所属名(日本語)                | :静岡大学創造科学技術大学院                                                  |

| Affiliation (English)   | :Graduate School of Science and Technology, Shizuoka University |

| キーワード/Keyword           | :「リソグラフィ・露光・描画装置」、「成膜・膜堆積」、「ドーピング」、「電気計測」                       |

## <u>1. 概要(Summary</u>

Recently, due to the miniaturization of devices, design and test of static random-access memories (SRAMs) has become increasingly more important in today's digital world. SRAM is the most common type of memory cell found in modern microprocessors. I designed the 6T SRAM by suing the layout editor tool and the fabrication of device was carried out by RNBS, Hiroshima University. Finally, the measurement of electrical characteristics was done.

<u>2. 実験(Experimental)</u>

## 【利用した主な装置】

Layout design tool, oxidation furnace, maskless lithography system, ion implantation equipment, well diffusion furnace, sputtering equipment (for Al), etching equipment (for ashing), PMA annealing furnace.

## 【実験方法】

After designing the circuit, the fabrication process are carried out as follows, i) N-well formation, ii) active-region formation, iii) source and drain formation, iv) formation of gate oxide film, v) contact hole formation and vi) Al electrode formation by using sputtering, maskless exposure system., etc.

## <u>3. 結果と考察(Results and Discussion)</u>

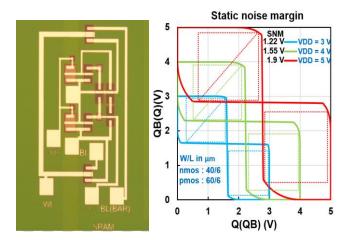

Fig. 1. shows the fabricated SRAM device. The W/L of nmos and pmos in  $\mu$ m are 40/6 and 60/6 respectively. Gate oxide thickness is 20 nm. The fabricated device is measured by using the probe station and semiconductor parameter analyzer

(SPA). Static noise margin (SNM) is a figure of merit for an SRAM cell. It can be extracted by nesting the largest possible square in the two voltage transfer curves (VTC) of the CMOS inverters, as shown in Fig. 2.

Fig. 1. Fabricated device Fig. 2. SNM of SRAM The SNM is calculated by varying the supply voltage (3, 4 and 5 V). For  $V_{DD} = 5$  V, the SNM is around 1.9 V. From the experimental evaluation, it is suggested that the SRAM is fabricated and functioning well as expected. In addition to SRAM, the ring oscillators with 3, 5 and 7 stages are also fabricated and evaluated successfully.

<u>4. その他・特記事項(Others)</u>

I would like to thank everyone in the RNBS, Hiroshima University. Special thanks to Prof. Shinji Yamada and Prof. Shin-ichiro Kuroki for their valuable guidance and support

<u>5. 論文·学会発表(Publication/Presentation)</u>

None

```

6. 関連特許(Patent)

```

None